本文

主要介绍多核体系结构,包括多核体系结构的由来,以及多和体系结构中的几大关键技术。

| 版本 | 说明 |

|---|---|

| 0.1 | 初版发布 |

参考

| 名称 | 作者 | 来源 |

|---|---|---|

| 《多核体系结构概览》 | 赵老师 | 培训 |

专业术语与缩略语

| 缩写 | 全称 | 说明 |

|---|---|---|

什么是多核体系结构

-

处理器设计的几大目标:

- 功能

- 性能

- 功耗

- 成本

- 其他

-

如何实现上述目标:体系结构

- 冯诺依曼体系结构:存储、程序、计算、控制

- Tomasulo算法、多发射、分支预测、预期、SIMD …

为什么需要多核体系结构

-

如何提高汽车产量?

- 流水线技术、多部件同时组装、优化配合

- 还能怎么做?多条生产线、多个工厂、批量化零件生产

-

怎么提高计算机系统性能?

- 提高单个处理器核的性能:并行性、局部性、可预测性;边际效应递减,功耗和面积的开销加大

- 还能怎么做?使用多个处理器核同时计算

- 为什么多核能提高性能?线程间的并行性

- 另一个促进因素:工艺技术的提高,可容纳更多晶体管资源

-

SoC:更高的集成度

- MCU、I/O、DSP、GPU、Crypto…

一个典型的ARM多核系统

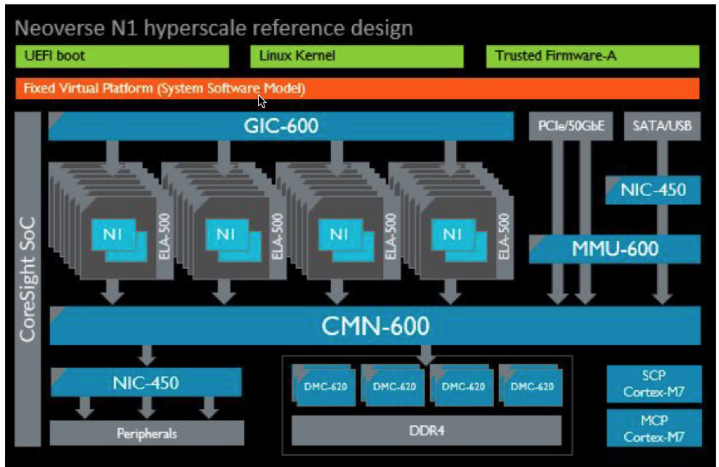

ARM N1 hyperscal reference design

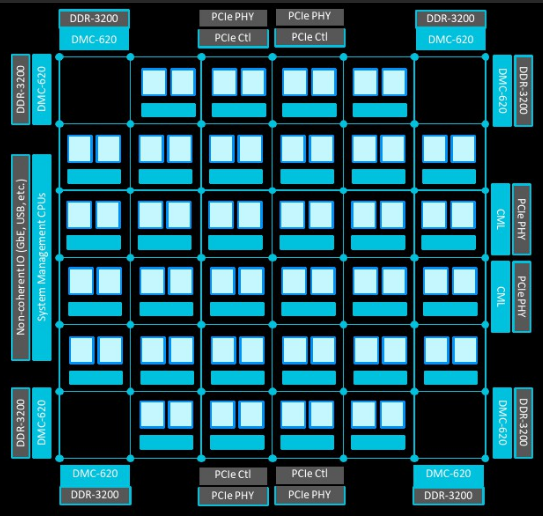

ARM N1 Floorplan View

多核体系结构关键问题

- 如何把多核连接起来?

- 如何保持一个统一的存储视图?

- 如何减少访存延迟?

- 如何控制中断在多个核之间的派发?

- I/O子系统

- 调试子系统

- 电源管理子系统

如何把多核连接起来

-

采用什么样的连接方式?

- 总线:链路负载重、带宽低

- XBar:带宽高、可扩展性差

- 交换式:Ring、Mesh

-

数据如何传输?

- 数据在相邻两个节点之间的可靠传输:链路层

- 数据在任意两个节点之间的可靠传输:网络层

- 设备节点间的高层语义模型(共享存储、消息传输):协议层

-

关键问题:

- Order的保证

- 死锁的避免

- 拥塞的控制

如何保持一个统一的存储视图

-

每个core都有自己的cache,怎么保证不同core间的cache内容不冲突?

- core0修改,core1不修改,core1是否能看到core0对x的修改?

- core0和core1都修改,会不会出现core0认为x=1,core1认为x=0的情况?

-

怎么可靠的通过共享存储在两个核之间传输数据?

- core0先写data,然后置flag=1,;core1先检查flag,然后读data;对硬件设计有什么影响?

- core0写x=1,core1看到了x=1并通知了core2,core2看到的x一定是1吗?

怎么减小访存延迟?

- 告诉缓存 cache

- 局部性:时间局部性和空间局部性

- cache自身也存在访问延迟和容量之间的权衡

- 使用多级cache,取得最小平均延迟

- 各级存储层次的带宽平衡问题

中断的派发

-

中断是一种slave主动向master发信息的方式

- 使能、优先级、中断状态管理、虚拟化

- Level Sensitive、Edge Triggered、Message Based

-

和单核系统的不同之处:

- 如何在多核之间派发中断?

- 如何避免一个核总是不响应中断?

- 如何防止多个核响应同一个中断?

I/O子系统

-

主要包含两类:

- On-Chip device:UART、I2C …

- PCI-Express subsystem

-

两个方向的通路:

- Master to Slave:PIO

- Slave to Master:DMA、Interrupt

-

主要的问题:

- Order:PIO order、PCIE order/deadlock

- I/O virtualization

调试子系统

-

软件写错了,如何调试?

- 暂停处理器执行:断点、观察点、单步执行

- 观察内部状态:读写寄存器、读写Memory

-

CPU硬件会定义相应的支持机制:

- 上述暂停机制、观察机制

- 调试器向CPU发送命令的通路

电源管理子系统

- 在某些组件闲置时将其降频、关时钟或断电,以节省功耗

- 监测机制:CPU核空闲,NoC接口空闲

- 控制机制:被控制组件和电源控制器间的握手协议

- 执行机制:PLL频率调节,电源关断

文章原创,可能存在部分错误,欢迎指正,联系邮箱 cao_arvin@163.com。