本文

主要介绍ARM DynamIQ架构下的功耗管理策略。

| 版本 | 说明 |

|---|---|

| 0.1 | 初版发布 |

参考

| 名称 | 作者 | 来源 |

|---|---|---|

| dsu_trm_100453_0002_00_en | ARM | ARM官网 |

| cortex_a75_trm_100403_0300_00_en | ARM | ARM官网 |

| AMBA低功耗接口(一)Q_Channel | lujun | 个人博客:骏的世界 |

专业术语与缩略语

| 缩写 | 全称 | 说明 |

|---|---|---|

| dsu | DynamIQ Shared Unit | DSU包含L3 Memory System、control logic、 external interfaces,以支持DynamIQ cluster 结构 |

| trm | Technical Reference Manual | 参考手册 |

| PMU | Power Management Unit | 功耗管理单元 |

| DVFS | Dynamic Voltage and Frequency Scaling | 动态电压和频率调节 |

背景

多核处理器

在早期的单核处理器中,往往通过提高时钟频率来提高性能,但随着频率的提高,设计难度会加大,性能提升效益却降低,以及功耗不断增大导致的散热问题,使得单核处理器性能提升越来越难,典型的就是Intel Pentium 4处理器。

多核处理器称为性能提升的最佳解决方案,也就是单芯片集成多个处理器核心,来替代复杂性较高的单线程处理器。通过多核的硬件结构,搭配多线程编程,使得处理器性能显著提升。在现代的多核硬件结构中,内存对多个CPU核是共享的,CPU核一般都是对称的,因此多核属于共享存储的对称多处理器(Symmetric Multi-processor,SMP)。

根据上文已知,多核处理器间共享内存,每个核处理一个进程,那么不同进程间并行执行就会遇到数据竞争的问题,如何解决数据竞争问题是多核处理器设计中的关键。

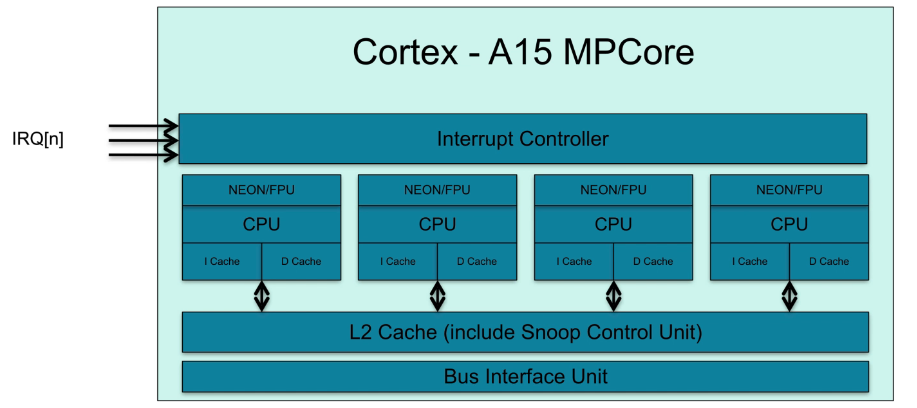

一般的cluster架构

- 一个cluster,最多4个对称的core。

- 每个core都有L1 Cache(D&I)。

- 程序运行在一个cluster中的core。

- cluster内有L2 cache,4个core共享。

- cluster内有snoop control unit,来维护L1 cache的数据一致性。

- cluster内有中断控制器,将中断信息分配给对应的cpu。

big.LITTLE架构

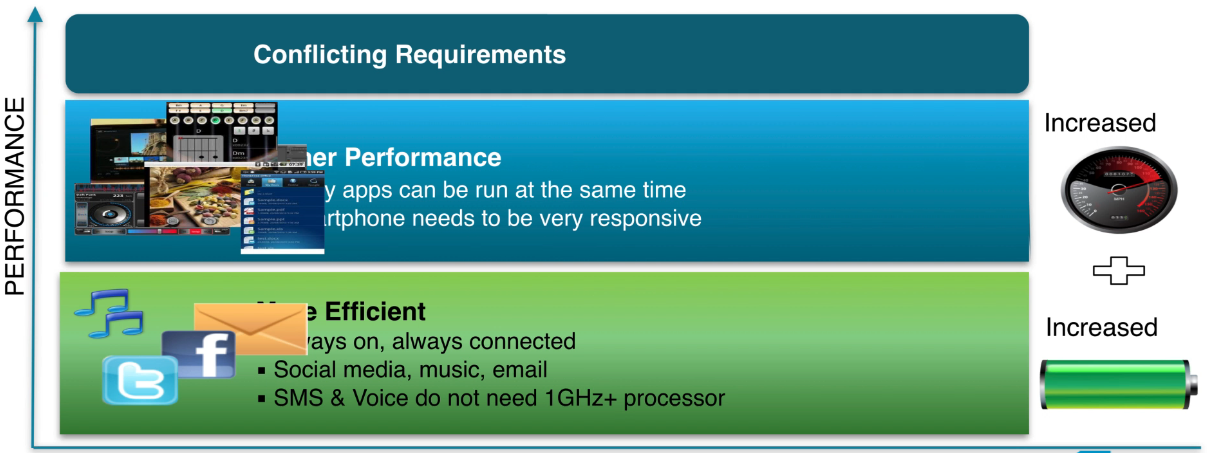

- 先来说一下为什么需要big.LITTLE架构?

- 从应用场景来分析,分为两类,一是对性能要求高,比如看打游戏,二是对性能要求不高,但尽可能降低功耗,如收发邮件。

- 大小核的设计,就是根据不同应用场景,来选用高性能核运行还是低功耗核运行。

- 典型的是低功耗核Coretex-A7和高性能核Coretex-A15,同属于ARMv7架构。

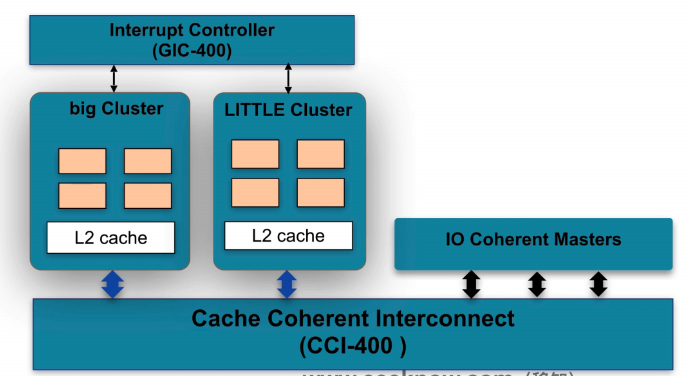

- 两个cluster,每个cluster最多4个对称的core。

- 每个core都有L1 Cache(D&I)。

- 程序运行在两个个cluster中的core。

- 每个cluster内有L2 cache,4个core共享。

- 每个cluster内有snoop control unit,来维护L1 cache的数据一致性。

- cluster之间通过互连和内存来维护cache数据一致性(CCI [Cache Coherent Interconnect])。

- 两个cluster共享一个中断控制器,将中断信息分配给对应的cluster,cluster再分配给对应的core。

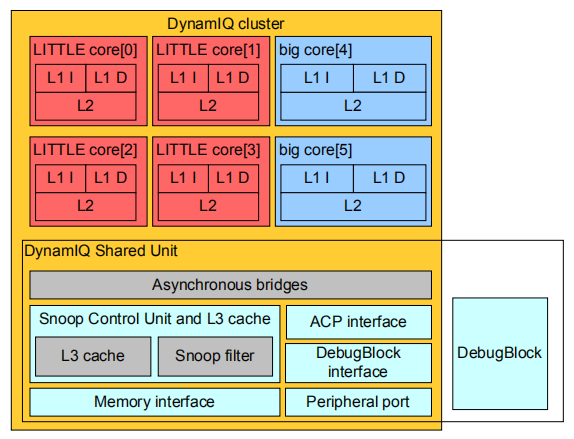

DynamIQ架构

- DynamIQ cluster结构中,可以将不同类型的core放到一个cluster中。比如,将性能高的core,和功耗低的core放进一个cluster。如果没有DynamIQ,需要将其放在2个不同cluster中的

- DynamIQ cluster结构中,增加了异步桥的设计,每个核可以工作在不同的频率,也可以单独的控制每个核开关。

- DynamIQ cluster结构中,core之间通过Shared Memory(L3 cache)来完成cache数据一致性。

- DynamIQ cluster结构中,共享一个中断控制器,将中断信息通过异步桥再分配给对应的core。

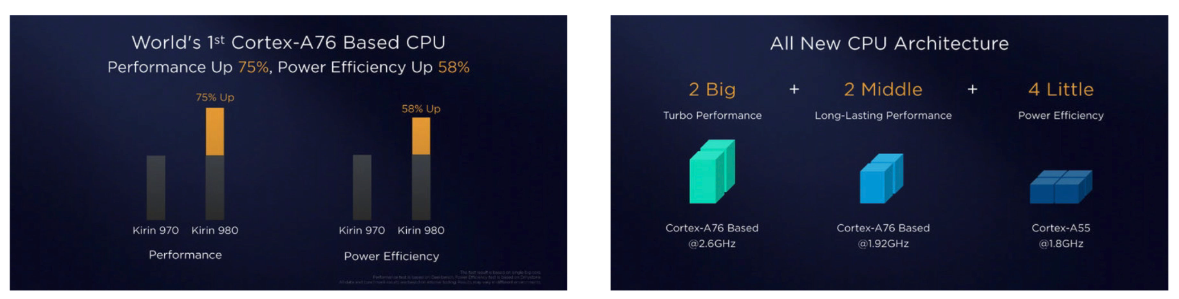

- 举例:Kirin 980

- Kirin 970采用传统的big.LITTLE,Kirin 980采用DynamIQ big.LITTLE。

- 性能提高75%,效能提高58%。

- 两个Big core,A76 2.6G

- 两个Middle core, A76 1.92G

- 四个Little core, A55 1.8G

Power domains

- DynamIQ cluster中对不同电源域可以采取上电/下电操作:

- 单个CPU core、L3 cache、cluster logic、debug。

- Cortex-A55还支持SIMD logic独立的电源域.

- 以上电源域在实现时可选择性实现。

dsu power modes

-

ON(Logic ON, RAMs ON) :

- 所有core和dsu logic开启。

- 仅通过必要的时钟门控降低动态功耗。

-

Functional retention(Logic ON, RAMs RET) :

- 在不访问L3 cache时,可将L3 cache置于retention状态(数据保持)。

- 暂停对L3 cache的访问,直到切换为ON状态,但core依然在运行。

- 可以通过任何一个cluster内的core,来禁用或启用dsu的fun_ret mode。

- 可以通过软件设定L3 cache进入fun_ret mode的超时值。

-

Memory retention(Logic RET, RAMs RET) :

- cluster的休眠模式。

- 关闭dsu logic,同时L3 cache数据保持。

- cluster内的所有core必须处于OFF(powerdown)状态。

- mem_ret mode不能维护cache一致性,所以需要在cluster外部无cache一致性维护需求的前提下开启(实际上,只有在cluster是唯一的active cluster时,才可以进入mem_ret mode)。

-

OFF(Logic OFF, RAMs OFF) :

- 关闭cluster内所有power domain。

- 当cluster请求关闭时,应先将L3 cache的数据更新到内存。

-

以上power mode低功耗深度依次增加 。

dsu power modes transitions

| Start mode | End mode | DSU behavior | Partner implemented behavior |

|---|---|---|---|

| OFF | ON | The L3 cache and snoop filter are initialized. The cluster is brought into coherency with the rest of the system. | Power applied, isolation disabled. |

| MEM_RET | ON | The cluster is brought into coherency with the rest of the system. | Power applied, isolation disabled. |

| MEM_RET | FUNC_RET | The cluster is brought into coherency with the rest of the system, but the RAMs remain in retention. | Power applied, clamps and isolation remain enabled. |

| ON | FUNC_RET | Waits for all memory transactions to complete. The clock to the retention domain is gated. L3 cache and snoop filter RAMs are put into retention. | RAM clamps and isolation enabled. |

| FUNC_RET | ON | L3 cache and snoop filter RAMs are taken out of retention. | RAM clamps and isolation disabled. |

| ON | OFF | Waits for all memory transactions to complete. L3 cache allocation is disabled. The L3 cache is cleaned and invalidated. The cluster is removed from system coherency. | DSU clamps and isolation to the rest of the system are enabled. |

| ON or FUNC_RET | MEM_RET | Waits for all memory transactions to complete. The cluster is removed from system coherency. This mode is only useful when the cluster is the only master active. | DSU clamps and isolation to the rest of the system are enabled. |

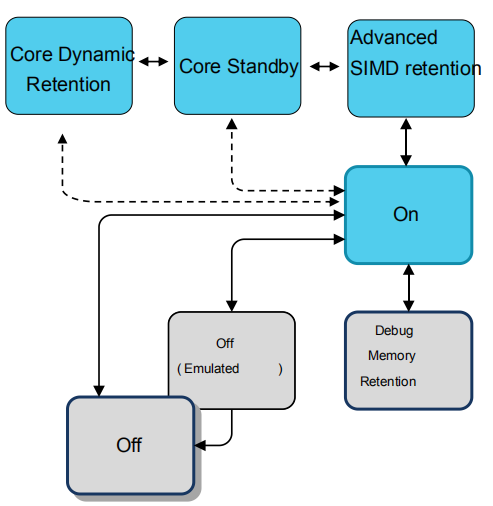

core power modes

-

ON :

- core已经启动,可以全面运行。

- 可以通过P-channel或tying PREQ LOW初始化为ON mode。

- 所有缓存均可访问且保持一致性。

-

Standby :

- core的待机模式,时钟树的顶部被添加时钟门控。

- 所有core logic和RAM处于retention状态。

- WFI和WFE指令,将core置于低功耗待机模式。

-

OFF :

- 全断电并且不保留任何状态,core logic和RAM关闭。

- OFF可以针对整个cluster,也可以针对单个core。

- cold reset可以在此模式对core进行reset。

- 可以通过P-channel将core初始化为此模式。

-

Off (emulated) :

- 所有core logic和RAM保持ON状态。

- 可以在外部声明core warm reset,以模拟断电场景,同时保持内核调试状态并允许调试访问。

-

Core dynamic retention :

- 所有core logic和RAM处于retention状态。

- 但是支持Snoop、GIC、debug访问。

-

Debug Memory Retention/Debug recovery :

- 可用于协助对外部watchdog触发的复位事件进行事后调试。

- 允许重置之前可以观察到重置之前存在的L1、L2 cache的数据。

- cache的数据将保留,并且在过渡回ON模式时不会更改。

-

Advanced SIMD retention (Cortex-A55 only) :

- SIMD logic处于retention状态,其余core逻辑不影响。

- 当需要在此模式下执行SIMD指令时,将暂停,直到内核进入开启模式为止。

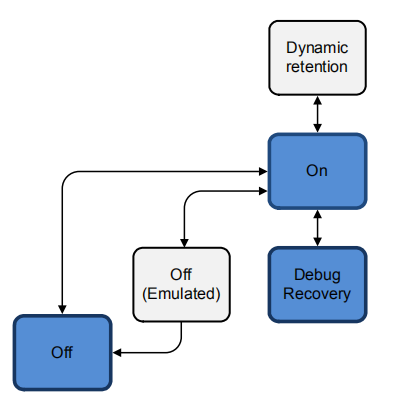

core power modes transitions

example for ARM Cortex-A75

About power management

Cortex-A75内核提供了功耗控制的动态和静态功机制:

-

Dynamic power management includes the following features:

- Architectural clock gating.

- Per-core Dynamic Voltage and Frequency Scaling (DVFS).

-

Static power management includes the following features:

- Dynamic retention.

- Powerdown

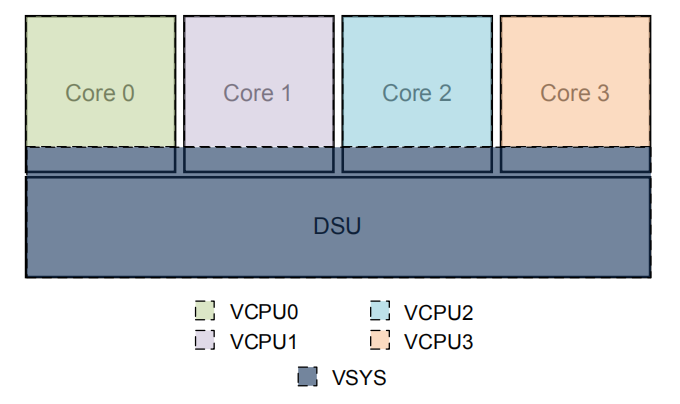

Voltage domains

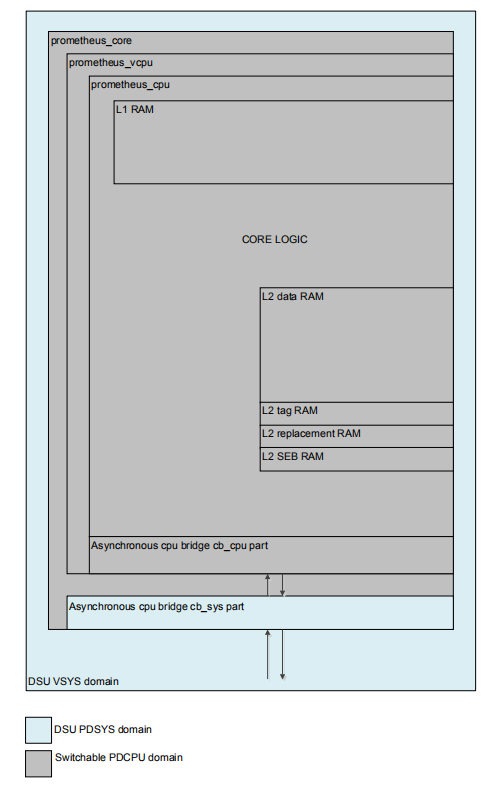

Cortex-A75内核支持VCPU电压域和VSYS电压域:

电压域之间存在异步桥逻辑。

- 异步桥的Cortex-A75核心逻辑和核心时钟域位于VCPU电压域中。

- 异步桥的DSU时钟域在VSYS电压域中。

Power domains

- PDCPU power domain:包括所有core logic,包括core内的异步桥logic。

- Advanced SIMD和floating-point单元属于PDCPU power domain,不支持额外独立的power domain。

- L1 and L2 RAMs属于PDCPU power domain,不支持额外独立的power domain。

- PDSYS power domain:包括dsu logic和异步桥logic。

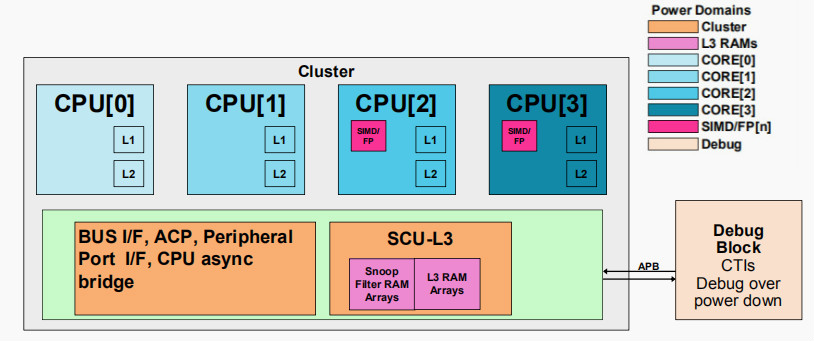

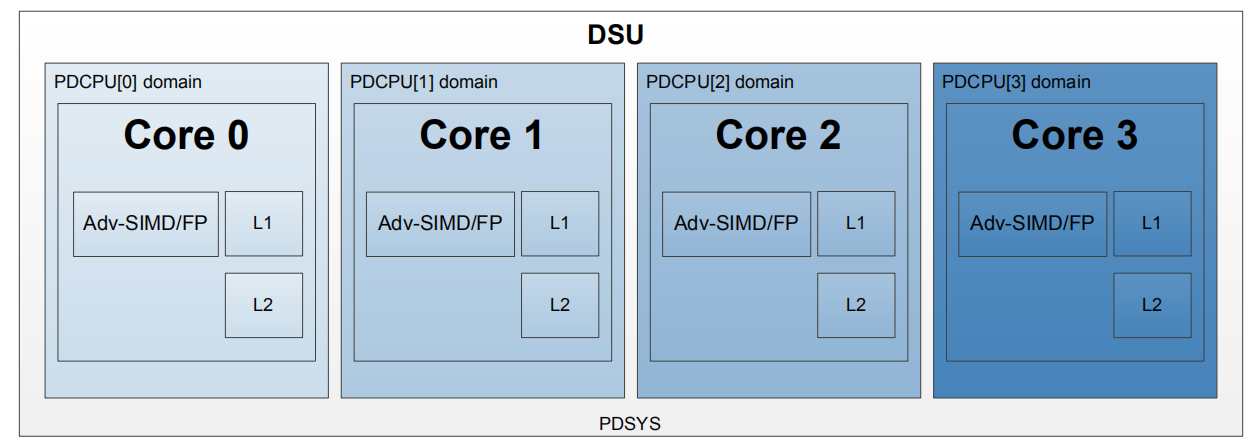

下图显示了cluster中的电源域,其中所有相同颜色的都属于同一个电源域。该示例显示了四个Cortex-A75内核。Cortex-A75内核的数量可以变化,并且域数量根据存在的Cortex-A75内核的数量而增加。

| Power domain | Descripti |

|---|---|

| PDCPU |

The domain includes the Advanced SIMD and floating-point block, the micro and main TLBs, L1 and L2 RAMs, and Debug registers associated with the Cortex-A75 core. |

| PDSYS | Top-level DSU power domain. |

Architectural clock gating modes(Standby)

Wait for Interrupt (WFI) and Wait for Event (WFE) are features of Armv8-A architecture that put the core in a low-power standby mode by architecturally disabling the clock at the top of the clock tree. The core is fully powered and retains all the state in standby mode.

Core Wait for Interrupt

当core执行WFI指令时,core将等待core内的所有指令retire,然后再进入低功耗状态。WFI指令确保以程序顺序retire在WFI指令之前发生的所有显式内存访问。此外,WFI指令可确保store指令已更新cache或已issue到L3 memory system。

当内核处于WFI低功耗状态时,如果检测到以下任何事件时,将临时启用core内的时钟,而不会导致core退出WFI低功耗状态:

- L3 memory snoop request

- A cache or TLB maintenance operation

- APB access to the debug or trace registers

- GIC CPU access through the AXI4 stream channel

发生以下情况之一时,发生从WFI低功率状态退出:

- WFI wake-up events.

- reset

Core Wait for Event

当core执行WFE指令时,core会等待core内的所有指令retire,然后再进入低功耗状态。如果设置了事件寄存器,则执行WFE不会导致进入待机状态,而是清除事件寄存器。

当内核处于WFE低功耗状态时,如果检测到以下任何事件时,将临时启用core内的时钟,而不会导致core退出WFE低功耗状态:

- L3 memory snoop request

- A cache or TLB maintenance operation

- APB access to the debug or trace registers

- GIC CPU access through the AXI4 stream channel

发生以下情况之一时,发生从WFE低功率状态退出:

- WFE wake-up events

- The EVENTI input signal is asserted

- reset

power control

所有power mode转换都是在电源控制器(PMU)的请求下执行的,使用P-channel接口与Cortex-A75内核进行通信。

每个core都有一个P-channel,而cluster有一个P-channel。 Cortex-A75 core可以通过 PACTIVE 发出当前power mode,电源控制器可以通过 PREQ 和 PSTATE 发出power mode的切换请求。然后,Cortex-A75 core在接受请求之前,执行达到请求的功耗模式所需的所有操作,例如门控时钟,刷新缓存或禁用一致性。

如果请求无效,或者是由于转换不正确,或者是因为状态已更改,使得状态不再合适,那么该请求将被拒绝。

具体控制协议参考P-channel。

Core power modes

下图显示了每个核心域P通道支持的模式,以及它们之间的合法转换:

具体各个power mode的含义,请参看上文介绍。

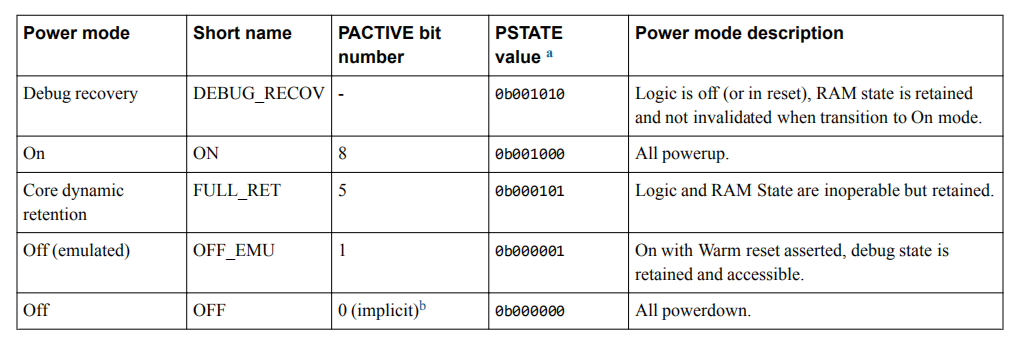

Encoding for power modes

下图展示了每个core P-channel支持的模式的编码:

Power domain states for power modes

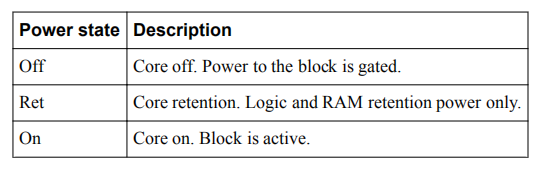

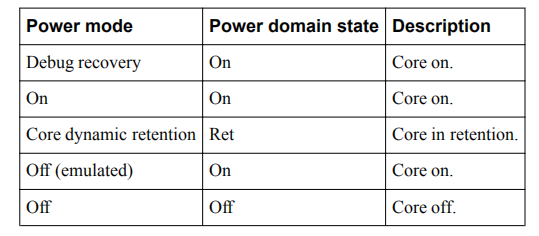

- Power state description:

- Supported core power domain states:

Power up and down sequences

Core powerdown

要使core 解除cache一致性,为core powerdown做好准备,必须执行以下掉电步骤:

- Save all architectural states.

- Configure the GIC distributor to disable or reroute interrupts away from this core.

- Set the CPUPWRCTLR.CORE_PWRDN_EN bit to 1 to indicate to the power controller that a powerdown is requested.

- Execute an ISB instruction.

- Execute a WFI instruction

在执行WFI之后,在电源控制器的指导下,所有L1和L2 cache禁用,L1和L2 cache刷新以及与L3 memory system的通信均在硬件中执行。

Core powerup

要在reset后使core保持cache一致性,不需要任何软件操作。

Debug over powerdown

Cortex-A75 core支持掉电调试,这使调试器即使在掉电后也能保持与core的连接。掉电调试逻辑是DebugBlock的一部分,它在cluster外部,在掉电调试过程中必须保持通电。

Q-channel

概述

AMBA提供了,低功耗的接口。用于实现power控制功能。目前,AMBA里面,包含2种低功耗接口。

- Q-Channel:实现简单的power控制,如上电,下电。

- P-Channel:实现更精细的power控制,如全上电,半上电,1/4上电等。

在一些场景下,组件只有两种power状态,分别为power-up,power-down。因此对这种组件的power控制,只需要对其上电,断电即可。用Q-Channel,即可实现。

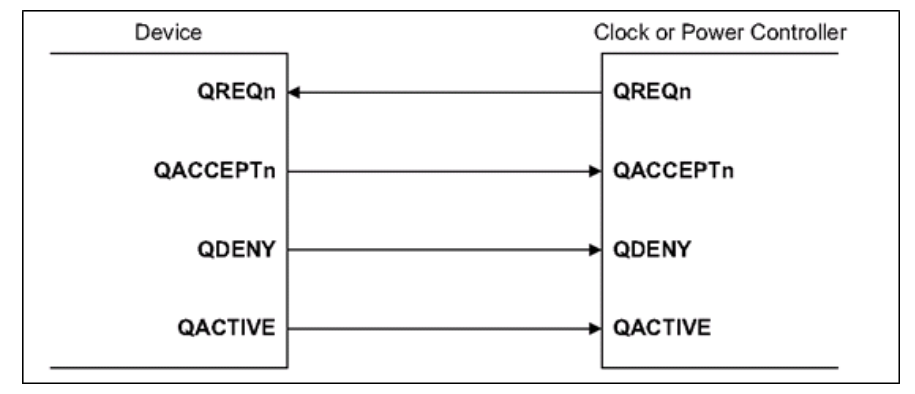

接口

以下是Q-Channel的接口:

分为device端和power controller端(下文均简称为PMU)。device端,就是需要被电源控制的组件,比如core,外设等。PMU端,就是提供电源管理的组件。

在Q-Channel中,将device的power状态,分成了2种,

- operational状态: device处于工作状态,简单理解为上电状态,下文称为上电状态

- quiescent状态:device处于停止状态,简单理解为断电状态,下文称为断电状态

接口如下

| 信号 | 说明 | 驱动端 |

|---|---|---|

| QREQn | power controller发送power请求信号,为高表示上电,为低表示断电 | PMU |

| QACCEPTn | 为高,表示device接受外部power请求 | Device |

| QDENY | 为高,表示device拒绝外部power请求 | Device |

| QACTIVE | 提供给device,向PMU发送power请求,更改自己的power状态,为高表示device需要PMU将自己置为上电状态,为低表示device需要PMU将自己置为断电状态 | Device |

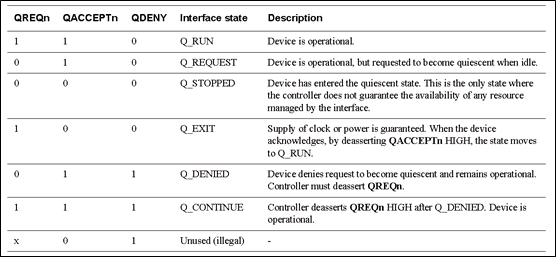

Q-Channel接口的握手状态

ARM对Q-Channel的interface,定义了几种握手状态:

- Q_RUN:device处于上电状态。

- Q_REQUEST:device处于上电状态,但是在idle状态时,可以接收power request,进入断电状态。

- Q_STOPPED:device进入了断电状态。

- Q_EXIT:等待被提供时钟或者power的状态。当device得到外部提供的时钟或者power时,将QACCEPTn拉高,进入Q_RUN状态。

- Q_DENIED: device拒绝外部power的请求,不进入断电状态,而保持上电状态。

- Q_CONTINUE:PMU在Q_DENIED状态后,将QREQn拉高后的状态。

以下是编码:

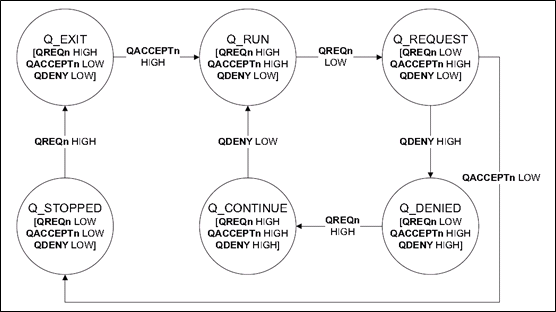

以下是状态转移图:

对于握手信号,有以下的规则:

- REQn只能在QACCEPTn为高并且QDENY为低时,才可以从高变为低。

- QREQn满足以下条件,才可以从低变为高:QACCEPTn和QDENY都为低;QACCEPTn和QDENY都为高。

- QACCEPTn只能在QREQn和QDENY都为低情况下,才可以从高变为低。

- QACCEPTn只能在QREQn和QDENY都为高情况下,才可以从低变为高。

- QDENY只能在QREQn和QACCEPTn都为高情况下,才可以从高变为低。

- QDENY只能在QREQn为低并且QACCEPTn为高情况下,才可以从低变为高。

Q_Channel的握手协议

device接受PMU的power请求

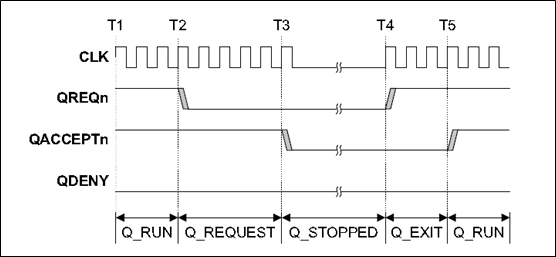

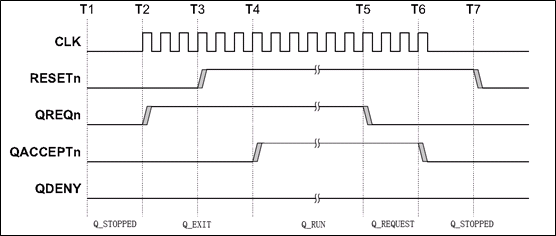

以下是握手协议时序图:

- 在T1,QREQn和QACCEPTn为高,Q_Channel进入Q_RUN状态。

- 在T2,QREQn为低,PMU请求device进入断电状态,然后等待外设响应,此时Q_Channel进入Q_REQUEST状态。

- 在T3,QACCEPTn为低,表示device接收PMU的请求,将自己进入断电状态。此时Q_Channel进入Q_STOPPED状态。

- 在T4,QREQn为高,PMU请求device进入上电状态,然后等待外设响应。此时Q_Channel进入Q_EXIT状态。

- 在T5,QACCEPTn为高,表示device接收PMU的请求,将自己进入上电状态。此时Q_Channel进入Q_RUN状态。

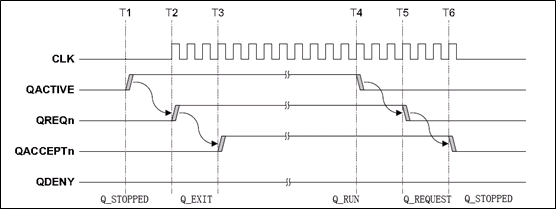

device拒绝PMU的power请求

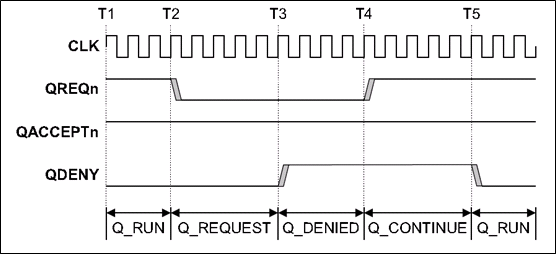

当外部PMU给device发送power请求,device可以拒绝该power请求。PMU收到device的拒绝响应后,应取消该power请求。

- 在T1,QREQn和QACCEPTn为高,Q_Channel进入Q_RUN状态。

- 在T2,QREQn为低,PMU请求device进入断电状态,然后等待外设响应,此时Q_Channel进入Q_REQUEST状态。

- 在T3,QDENY为高,表示device拒绝PMU的请求,自己保持上电状态。此时Q_Channel进入Q_DENIED状态。

- 在T4,PMU接收到device的拒绝响应,将QREQn拉高,PMU请求device进入上电状态,然后等待外设响应。此时Q_Channel进入Q_CONTINUE状态。

- 在T5,QDENY为低,表示device接收PMU的上电请求,将自己保持上电状态。此时Q_Channel进入Q_RUN状态。

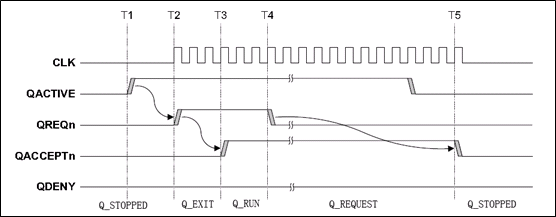

device复位信号与Q_Channel的结合

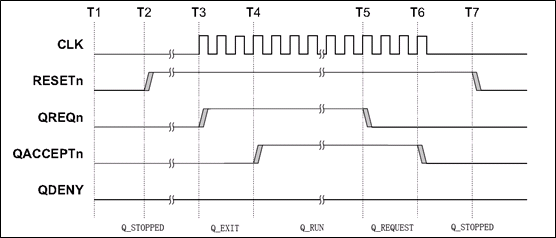

复位信号,需要和Q_Channel的信号,进行组合。一般来说,复位信号,也会由PMU来控制。

RESETn复位有效时,QREQn为低

- T2时刻,RESETn为高,复位取消。

- T3时刻,QREQn为高,PMU向device请求上电。Q_Channel进入Q_EXIT状态。

- T4时刻,QACCEPTn为高,device接受PMU的上电请求。Q_Channel进入Q_RUN状态。

- T5时刻,QREQn为低,PMU向device请求断电,Q_Channel进入Q_REQUEST状态。T6时刻,QACCEPTn为低,device接受PMU的断电请求。Q_Channel进入Q_STOPPED。

- T7时刻,将RESETn拉低。

RESETn复位有效时,QREQn为高

- T2时刻,QREQn拉高,PMU向device请求上电。Q_Channel进入Q_EXIT状态。

- T3时刻,因为RESETn为低,复位有效,device将QACCEPTn保持为低,Q_Channel保持Q_EXIT状态。

- T4时刻,因为RESETn为高,复位无效。device将QACCEPTn拉低,响应PMU的上电请求。Q_Channel进入Q_RUN状态。

- T5时刻,QREQn拉低,PMU向device请求断电,Q_Channel进入Q_REQUEST状态。

- T6时刻,device将QACCEPTn拉低,响应PMU的断电请求。Q_Channel进入Q_STOPPED状态。

- T7时刻,RESETn拉低。

QACTIVE

QACTIVE,是提供给device,给PMU发送power请求的信号。可以由多个来源的组合。如果为高,那么PMU要给自己上电,并且之后,不能给自己断电。

QACTIVE和握手信号(QREQn,QACCEPTn,QDENY)是独立开的。

请求上电和请求下电

- T1时刻,device将QACTIVE拉高,向PMU发起退出断电请求。

- T2时刻,PMU将QREQn拉高,Q_Channel进入Q_EXIT状态。

- T3时刻,进入Q_RUN状态。

- T4时刻,device将QACTIVE拉低,device向PMU发起进入断电请求。

- T5时刻,PMU将QREQn拉低,Q_Channel进入Q_REQUEST状态。

- T6时刻,进入Q_STOPPED状态。

PMU不允许断电

- T1时刻,device将QACTIVE拉高,向PMU发起上电请求。

- T2时刻,PMU将QREQn拉高,Q_Channel进入Q_EXIT状态。

- T3时刻,进入Q_RUN状态。之后,device处于上电状态。

- T4时刻,PMU将QREQn拉低,PMU想让device进入断电状态,但是QACTIVE为高,表示device要一直处于上电状态。因此QACCEPTn持续保持高,Q_Channel一直维持在Q_REQUEST状态。device维持在上电状态。

- T5时刻,因为之前QACTIVE拉低,device想进入断电状态,device将QACCEPTn拉低,响应PMU的断电请求,然后Q_Channel进入Q_STOPPED状态。device进入断电状态。

P-channel

概述

为了满足复杂的power管理的需求,ARM提供了P-Channel的低功耗接口,来满足这样的应用场景。

P-Channel,提出了一个概念,叫power state transition。在P-Channel的应用场景中,power的状态有很多,这个是实现是自己定义的。power的各个状态之间,是可以切换的。

2个最基本的状态:

- lower-power状态:在这个状态下,power消耗比较少,device处于低功耗状态(具有部分功能)

- higher-power状态:在这个状态,power消耗比较大,device处于正常状态(具有完整功能)

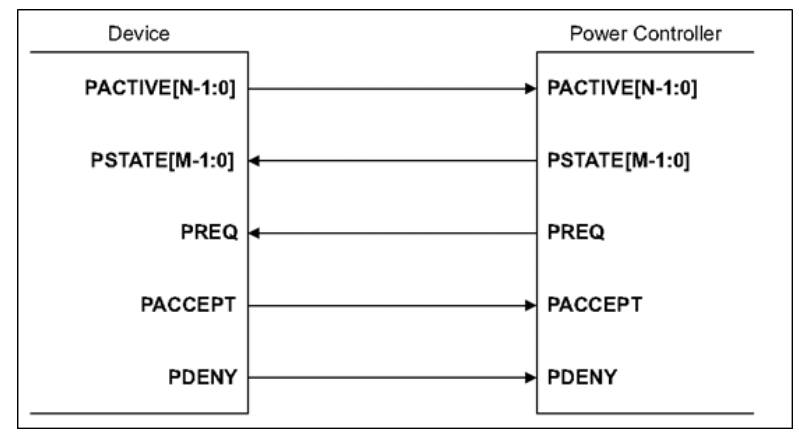

接口

分为device端和power控制端(下文简称PMU)。

| 信号 | 说明 | 驱动端 |

|---|---|---|

| PACTIVE [N-1:0] | 提供wakeup功能 | device |

| PSTATE [M-1:0] | 需要切换的目的power状态 | PMU |

| PREQ | 为高,表示power状态切换请求 | PMU |

| PACCEPT | 为高,表示device接受power状态切换请求 | device |

| PDENY | 为高,表示device拒绝power状态切换请求 | device |

- PACCEPT和PDENY在握手中,只能有一个为高。

- PACCEPT表示接受请求,PDENY表示拒绝请求。

- PACCEPT,PDENY,PREQ,PSTATE,必须是从寄存器直接输出。

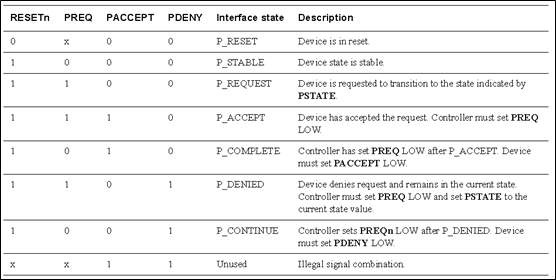

P_Channel接口握手状态

-

对P_Channel的接口,arm也定义了一些握手状态:

- P_RESET: device处于reset状态

- P_STABLE: device处于非reset状态,并且PMU没有发送power状态切换请求

- P_REQUEST: PMU向device发送power状态切换请求

- P_ACCEPT: device接受PMU的power状态切换请求

- P_DENIED: device拒绝PMU的power状态切换请求

- P_COMPLETE: device接受PMU的power状态切换请求后,PMU取消power状态切换请求

- P_CONTINUE: device拒绝PMU的power状态切换请求后,PMU取消power状态切换请求

-

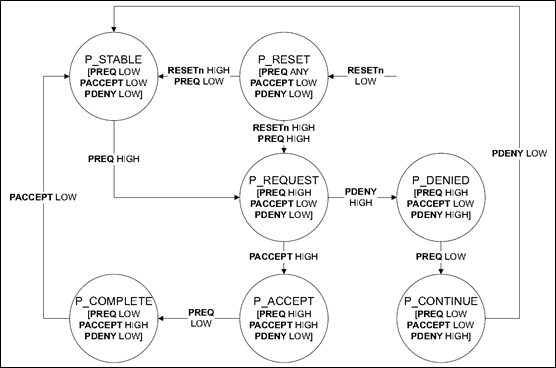

编码规则:

- 状态转移图:

- 握手协议规则:

- PREQ只有在PACCEPT和PDENY都为低情况下,才可以从低变为高

- PREQ要满足以下的任意条件,才可以从高变为低:1)PACCETP是高,PDENY为低;2)PACCEPT为低,PDENY为高。

- PSTATE满足以下的任意条件,才可以变化:1)PREQ,PACCEPT,PDENY都为低;2)PREQ和PDENY为高,PACCEPT为低。

- PACCEPT只有在PREQ为高,并且PDENY为低,才可以从低变为高。

- PACCETP只有在PREQ为低,并且PDENY为低,才可以从高变为低。

- PDENY只有在PREQ为高,并且PACCEPT为低,才可以从低变为高。

- PDENY只有在PREQ为低,并且PACCEPT为低,才可以从高变为低。

P_Channel的握手协议

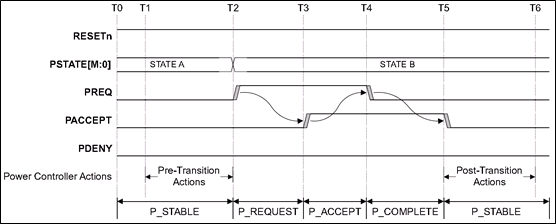

- device接受power状态切换:

- 在T2时刻之前,P_Channel处于P_STATBLE状态。

- T2时刻,PMU拉高PREQ,将PSTATE置为STATE B。向device发送power状态切换请求,请求将device切换到STATE B的power状态。P_Channel进入P_REQUEST状态。

- T3时刻,device将PACCEPT拉高,表示接受PMU的power状态切换请求。P_Channel进入P_ACCEPT状态。

- T4时刻,PMU接收device的PACCEPT响应,拉低PREQ,取消请求。P_Channel进入P_COMPLETE状态。

- T5时刻,device将PACCEPT拉低,表示完成power状态切换。P_Channel进入P_STABLE状态。

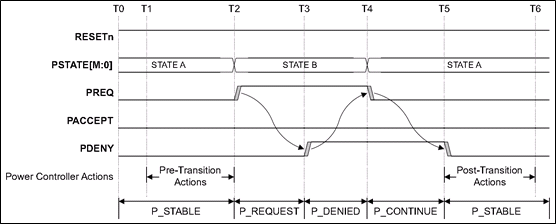

- device拒绝power状态切换:

- T2时刻以前,P_Channel处于P_STABLE状态。

- T2时刻,PMU将PREQ拉高,将PSTATE置为STATE B。向device发送power状态切换请求,请求将device切换到STATE B的power状态。P_Channel进入P_REQUEST状态。

- T3时刻,device将PDENY拉高,表示拒绝PMU的power切换请求。P_Channel进入P_DENIED状态。

- T4时刻,PMU接收到device的PDENY响应,将PREQ拉低,取消请求,并且把PSTATE置为STATE A。P_Channel进入P_CONTINUE状态。

- T5时刻,device将PDENY拉低,P_Channel进入P_STABLE状态。

device的复位和初始化

device在复位时,必须将PACCEPT和PDENY置为低,但对PACTIVE没有要求。P_Channel的状态为P_STABLE时,device的复位信号,才可以设置为有效。当device的复位无效时,device要进入初始化,此时PMU要设置PSTATE信号值,device会在复位之后,采样该信号值,从而采用合适的初始化流程。PSTATE要在复位信号无效后要保持稳定。device,要提供一个初始化周期时间,tinit。用来表示,复位之后,PSTATE需要保持多久时间,供device初始化使用。PSTATE在tinit时间之内,必须要保持稳定。

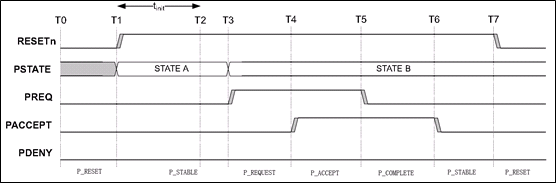

- 上面是时序图:

- T1时刻之前,RESETn为低,复位有效,P_Channel处于P_RESET状态。

- T1时刻,RESETn为高,PMU将PSTATE置为STATE A。P_Channel进入P_STABLE状态。

- T2时刻,由于tinit的限制,PMU要将PSTATE一直保持在STATE A,以便device正确的初始化。device必须要在tinit时间内,采样PSTATE。此后,PMU就可以发送power切换请求了。

- T3时刻,PMU将PREQ置高,并且将PSTATE置为STATE B,发送power切换请求。P_Channel进入P_REQUEST状态。

- T4时刻,device将PACCEPT拉高,表示接受PMU的power状态切换请求。P_Channel进入P_ACCEPT状态。

- T5时刻,PMU接收device的PACCEPT响应,拉低PREQ,取消请求。P_Channel进入P_COMPLETE状态。

- T6时刻,device将PACCEPT拉低,表示完成power状态切换。P_Channel进入P_STABLE状态。

- T7时刻,P_Channel在P_STATBLE状态,可以进行复位,外部拉低RESETn,P_Channel进入P_RESET状态。

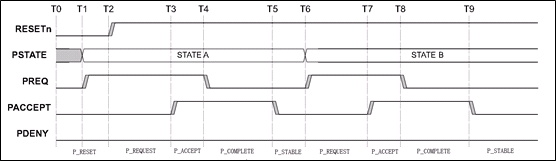

- 上图展示了,当复位时,PMU发送power切换情况的时序图。

- T1时刻,PMU将PREQ拉高,并置PSTATE为STATE A,但是复位信号有效,device不接收PMU请求。P_Channel保持为P_RESET状态。

- T2时刻,复位信号释放,因为PREQ为高,P_Channel进入P_REQUEST状态。device接收PMU的power切换请求。

- 之后的就和上面的分析原理是一样的了。

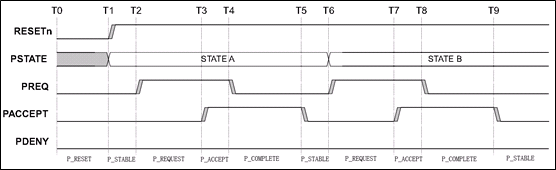

- 上图展示了,复位后,PMU发送使device进入STATE A的power状态请求,当该转换完成后,PMU又继续发送使device进入STATE B的power状态请求。

- PMU在发送下一个power切换请求前,必须保证上一个power切换请求,传输完毕。

多个power状态切换

- 在T0,device处于STATE A状态。

- 在T1到T4,通过P_Channel,使device进入STATE B状态。在T4,P_Channel进入P_STABLE状态。

- 在T5-T8,通过P_Channel,使device进入STATE C状态。在T8,P_Channel进入P_STABLE状态。

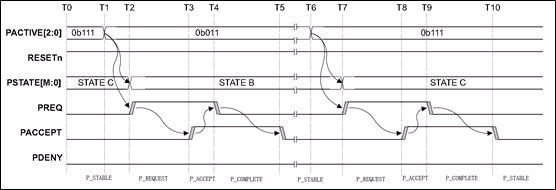

PACTIVE

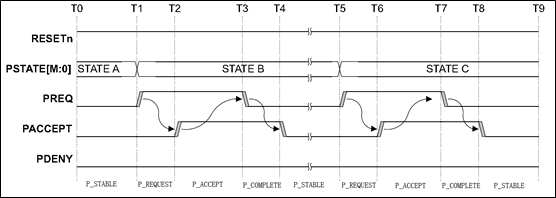

PACTIVE,提供给device给PMU发送请求。PACTIVE的每一个bit,表示一种请求。bit为高,表示device发送请求给PMU,让PMU处理,bit为低,表示device没有发送请求给PMU处理。PACTIVE和握手协议,是独立开的。PACTIVE是设计自定义的,请求完全自己定义。当然,也可以不使用PACTIVE,如果不是用PACTIVE,需要将PACTIVE置为0。

- 上图是PACTIVE的例子:

- PACTIVE有3个bit,每个bit,映射到一个power状态,MSB具有高优先级:1)PACTIVE[2]:STATE C;2)PACTIVE[1]: STATE B;3)PACTIVE[0]: STATE A。

- T1时刻,device将PACTIVE设置为3’b011,表示device向PMU发送power切换请求,将自己切换为STATE B。

- PMU接收到device的请求后,从T2到T5,向device发送power切换请求,并且切换到STATE B状态。最后P_Channel进入P_STABLE状态。

- T6时刻,device将PACTIVE设置为3’b111,表示device向PMU发送power切换请求,将自己切换为STATE C。

- PMU接收到device的请求后,从T7到T10,向device发送power切换请求,并且切换到STATE C状态。最后P_Channel进入P_STABLE状态。

device需要提供的信息

为了PMU的设计的正确性,device需要向PMU提供以下的一些信息:

- device支持的power状态,包括以下:

- PSTATE定义和编码

- PACTIVE每个bit代表的请求

- 用于初始化power状态,推荐的PACTIVE输出

- PACTIVE需要被忽略,或者一直置0的bit信息

- power状态的切换,包括以下:

- power状态切换之后的device行为

- device拒绝power状态切换的条件

- 复位释放后,用于初始化device的PSTATE的合理值

- T_init的值

文章原创,可能存在部分错误,欢迎指正,联系邮箱 cao_arvin@163.com。